锁相环(PLL)

PLL介绍

锁相环(PLL)的概念在1930年代初首次出现。但是,这项技术现在没有发展,发展这种技术的成本因素非常高。自集成电路领域的进步以来,PLL已成为电子技术的主要建筑块之一。在目前,PLL作为SE / NE560系列(560,561,562,564,565和567)中的单个IC可用,以进一步降低购买成本,分立IC用于构建PLL。

PLL应用程序

- 频率调制(FM)立体声解码器,FM解调网络FM操作。

- 频率合成提供参考信号频率的倍数。

- 用于电动机的控制,跟踪过滤器。

- 用于频移键控(FSK)解码用于解调载波频率。

PLL框图

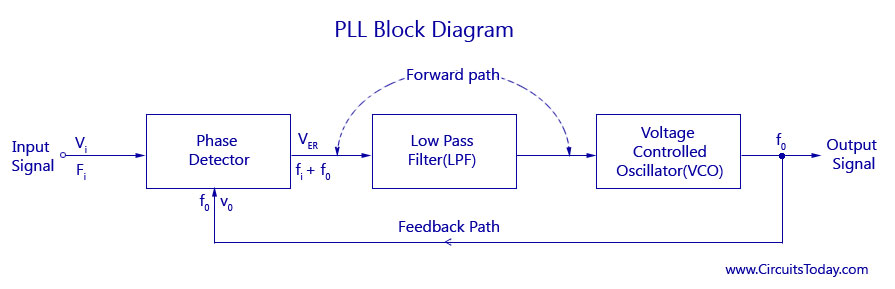

基本PLL的框图如下图所示。它基本上是由相位检测器,低通滤波器(LPF)和电压控制振荡器(VCO)组成的触发器。

具有输入频率fi的输入信号VI通过相位检测器。相位检测器基本上是比较器,该比较器将输入频率与反馈频率FO的输入频率进行比较。相位检测器提供输出误差电压Ver(= Fi + Fo),这是直流电压。然后将该直流电压传递给LPF。LPF消除了高频噪声,并产生稳定的DC电平VF(= FI-FO)。VF还表示PLL的动态特性。

然后将DC电平传递给VCO。VCO(FO)的输出频率与输入信号成比例。通过反馈回路比较和调整输入频率和输出频率,直到输出频率等于输入频率。因此,PLL在这些阶段工作 - 自由运行,捕获和锁相。

顾名思义,自由运行阶段在没有施加输入电压时指的是阶段。一旦施加输入频率,VCO就开始改变并开始产生输出频率以进行比较,则该阶段称为捕获阶段。一旦调整输出频率,频率比较会停止变得等于输入频率。此阶段称为锁相状态。

现在让我们详细研究PLL的各个部分 - 相位检测器,低通滤波器和电压控制振荡器。

阶段探测器

该比较器电路比较输入频率和VCO输出频率,并产生与两个频率之间的相位差成比例的DC电压。PLL中使用的相位检测器可以是模拟或数字式。尽管大多数单片PLL集成电路使用模拟相位检测器,但大多数离散相位检测器都是数字类型。最常用的模拟相位检测器之一是双平衡混频器电路。一些常见的数字式相位检测器是

1.1独家或相位检测器

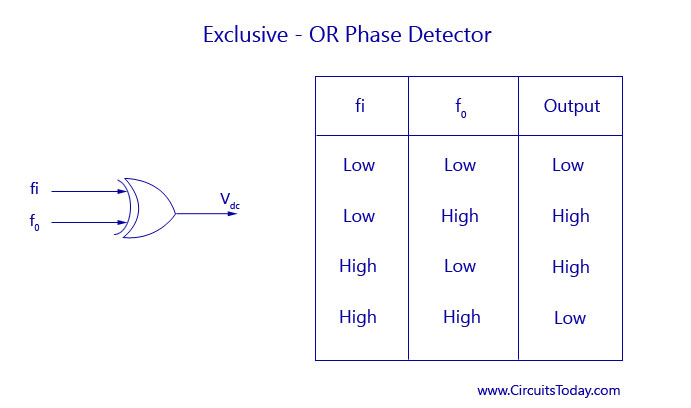

单个或相位检测器如下图所示。

它作为4070型的CMOS IC获得。频率都被提供为EX或相位检测器的输入。遵守输出的ex-or概念只有在输入文件中的任一输入或fo变高时才能变高。所有其他条件都会产生低输出。让我们考虑输入频率通过θ度引导输出频率的波形。也就是说,fi和fo具有θ度的相位差。比较器的直流输出电压将是其两个输入之间的相位差的函数。

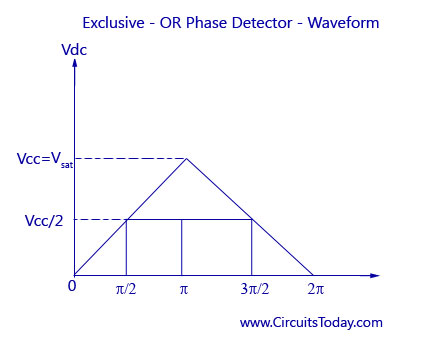

该图显示了DC输出电压的曲线图作为FI和FO之间的相位差的函数。当相位检测器为180°时,输出直流电压最大。当FI和FO是方波时,使用型相位检测器。

1.2边缘触发相位检测器

当FI和FO是具有少于50%的占空比时使用边缘触发的相位检测器。使用R-S触发器的这种相位检测器的图示如下所示。两个NOR门(CD4001)交叉耦合以形成R-S触发器。相位检测器的输出通过触发R-S触发器来改变它的逻辑状态。也就是说,相位检测器的输出在输入FI和FO的正边缘上改变其逻辑状态。可以从下图中理解这种检测器的优点。显然,直流输出电压在360°上线性。

1.3单片相位检测器

单片式相位检测器使用CMOS型4044 IC,这是忽略谐波灵敏度和占空比问题的高处,电路将仅响应输入信号中的转换。这是关键应用中最优选的相位检测器,因为相位误差和输出误差电压与输入波形的幅度和占空比的变化无关。

2.低通滤波器(LPF)

低通滤波器(LPF)用于锁相环(PLL),以摆脱相位检测器的输出中的高频分量。它还消除了高频噪声。所有这些功能使LPF成为PLL中的关键部分,并有助于控制整个电路的动态特性。动态特性包括捕获和锁定范围,带宽和瞬态响应。锁定范围是跟踪范围,其中PLL系统的频率范围遵循输入频率的变化。捕获范围是相锁圈循环达到相位锁的范围。

当滤波器带宽减小时,响应时间增加。但这会减少捕获范围。但它也有助于减少噪声,并通过瞬间损失保持锁定的环路。两种类型的无源滤波器用于PLL中的LPF电路。还使用放大器,其中LPF获得增益。PLL中使用的有源滤波器如下所示。

3.压控振荡器(VCO)

VCO的主要功能是产生与输入电压成正比的输出频率。SE / NE 566 VCO的连接图如下图所示。VCO的高频率为500 kHz。

该VCO提供了同时方波和三角波输出作为输入电压的函数。振荡频率由电阻器R和电容器C确定施加到控制端子的电压Vc。

单片相锁环

PLL现在随时可用作IC,在SE / NE 560系列中开发。其中一些常用的常用项是SE / NE 560,561,562,564,565和567.它们中的每一个之间的差异在不同的参数中,如运行频率范围,电源要求和频率和带宽范围。除了所有的系列中,SE / NE 565是最着名的。它可作为14针浸渍,也可作为10针金属封装包装。下面给出了14针浸和其特性。

单片PLL特征

- 工作频率范围:0.001 Hz至500 kHz。

- 工作电压范围:±6至±12 V.

- 输入阻抗:通常为10 k Q。

- 输出槽电流:通常为1MA。

- 输出源电流:通常为10 m a。

- VCO中心频率漂移温度:通常为300ppm /°C。

- VCO中心频率漂移,电源电压:最大1.5%/ v。

- 跟踪所需的输入电平:10 MVRMS最小到3 V峰到峰值最大。

- 带宽调整范围:<±1至>±60%。

框图和连接图如下图所示。

框图由相位检测器组成,其用作相位比较器,放大器和低通滤波器,以及电阻器(3.6千克欧姆)和电容器C2的组合。放大器的输出被送回VCO。表示IC的不同引脚也在框图中示出。引脚1和10是正极和负供应销。引脚2和3是对相位检测器的输入。输入信号通过差分模式通过这些引脚馈送。引脚4是VCO输出,引脚5是相位比较器VCO输入。如果两个引脚都短短,则VCO的输出将被提供回相位比较器。相位比较器的输出给出放大器。放大器具有两个输出,其作为解调器输出(引脚7)和参考输出(引脚6)作为解调器输出(引脚6)。 An LPF circuit is formed by connecting the capacitor C2 between pin 7 and 10 with a resistor of value 3.6 kilo ohms. The value of C2 must be large enough to eliminate the variations in demodulated output and stabilize the VCO frequency.

引脚8和9用于连接外部电阻(R1)和外部电容器(C1)。R1和C1的值有助于调整PLL的自由运行频率(FR)。虽然C1的值可以是任何东西,但电阻器R1的值必须具有2到20千克欧姆之间的值。所有这些因素都可用于确定PLL的中心频率。

PLL的自由运行频率为FR =(1.2)/(4R1C1)赫兹

PLL的锁定范围被给出为Flock =(+/-){(8fr)/ v}赫兹

PLL的捕获范围是Fc =(植绒/ [2 * 10 ^ 3 * c2])^ 1/2

锁定范围通常随着输入电压的增加而增加,但随着电源电压的增加而下降。

锁相环(PLL) - 工作

让我们考虑自由运行频率来成为FR。让FR成为电压控制振荡器(VCO)在没有输入信号的情况下运行的频率。让输入信号Fi从零增加增加到相位比较器。

误差电压和输入频率之间的图形如下所示。可以看出,当输入频率小于FI1时,误差电压ver减小到零。此时,VCO将以自由运行频率运行,FR。当输入频率,FI增加并达到FI1时,误差电压从零跳跃到负电压。该值将等于输入频率和实际VCO输出频率(FI - FO)之间的差异。然后通过滤波,放大和向VCO的控制端子进行滤波,放大和施加扩增电压Vd来处理该结果误差电压。

VCO的瞬时频率降低,因为fo落在VD的负值并增加VRF的正值。在某些时候,VCO的频率降低等于Fin1(捕获范围的下边缘),然后锁定结果,以及输出信号频率

VCO可以等于输入信号频率(即,FO = FI)。VCO频率锁定输入信号频率,最多可达FI2(锁定范围的上端)。如果输入信号频率超过FI2,则误差电压Vg将均降至零,并且VCO将在自由运行频率fR处运行,如图所示。如果输入信号频率现在慢慢扫回,并且它达到FD1的值,那么环路(VCO频率)锁定具有输入信号频率,导致误差电压Ver的正跳跃。因此,VCO输出频率连续从FR速度增加,直到FO变得等于FI。VCO频率FO锁定输入信号频率达到FD2(锁定范围的下边缘),如图所示。现在,如果输入信号的频率下降到FD2以下,则误差电压Ver将均降至零,VCO将以自由运行频率运行。

9.注释

文章中提到的图形和图在哪里?

PLL和相位检测器的用途是什么?

这是有用的文章,非常感谢你,但是你能附上并添加参考资料,再谢谢你

。

很好的解释

题。我一直在审查PLL并发现我无法理解一件事:VCO将频率取决于输入电压,因此需要稳态非零电压,以将其拉出其自由运行频率。另一方面,来自LPF的输出是当相位匹配时达到零幅度的正弦曲线,无论频率如何匹配。偏移电压在哪里可以在循环被锁定时维护新的VCO频率?

这么精彩而简单的解释。感谢您的帮助。

对这个重要主题的良好介绍。

我是最后一年的学生。你能在嵌入式系统中建议我一个项目的想法吗?

罗博特