在本文中,让我们了解数字电子中使用的不同类型的触发器。

数字电子的基本Flip - flop

本文讨论了基本的触发器电路,如S-R触发器、J-K触发器、D触发器和T触发器,以及真值表和它们相应的电路符号。

在进入主题之前,了解它的基础知识是很重要的。点击下面的链接获取更多信息。

看一看:布尔逻辑

看一看:逻辑门

看一看:半加法器和全加法器

触发器实际上是逻辑门的一种应用。借助布尔逻辑,您可以使用它们创建内存。触发器也可以被认为是随机存取存储器(RAM)的最基本概念。当给它们一个特定的输入值时,如果逻辑门设计正确,它们将被记住并执行。触发器的广泛应用有助于设计更好的电子电路。

触发器最常用的应用是在反馈电路的实现中。由于内存依赖于反馈的概念,可以用触发器来设计它。

在电子电路中主要有四种类型的触发器。他们是

- 基本的触发器或S-R触发器

- 延迟触发器[D触发器]

- j - k触发器

- T触发器

1.因此触发器

SET-RESET触发器是在两个NOR门和两个NAND门的帮助下设计的。这些触发器也被称为S-R锁存器。

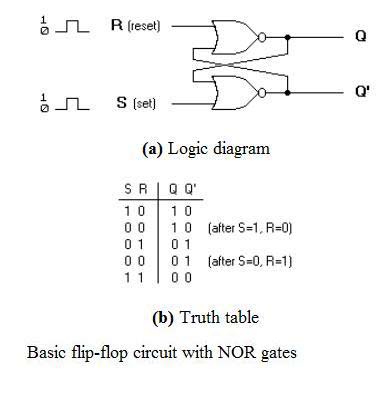

使用NOR门的S-R触发器

这种触发器的设计包括两个输入,称为SET [S]和RESET [R]。还有两个输出,Q和Q '。图和真值表如下所示。

从图中可以明显看出,触发器主要有四种状态。他们是

S = 1, R = 0-Q = 1,问' = 0

这种状态也称为设置状态。

S = 0, R = 1 Q = 0, Q ' = 1

这种状态称为RESET状态。

在这两种状态下,你可以看到输出是互相补充的Q的值跟随着S的值。

S=0 R=0 - Q Q ' =记住

如果S和R的值都被转换为0,那么电路就会记住S和R在它们之前的状态。

S=1, R=1 - Q=0, Q ' =0[无效]

这是无效状态,因为Q和Q'的值均为0。他们应该互相称赞。通常,必须避免这种状态。

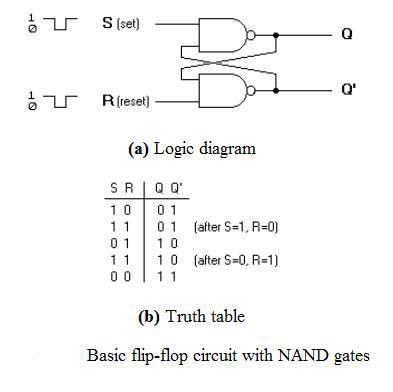

使用与非门的S-R触发器

使用与非门的S-R触发器电路及其真值表如下所示。

和NOR门S-R触发器一样,这个触发器也有四种状态。他们是

S = 1, R = 0-Q = 0, Q ' = 1

这种状态也称为设置状态。

S = 0, R = 1 Q = 1,问' = 0

这种状态称为RESET状态。

在这两种状态下你可以看到输出是互补的Q的值跟随着S的互补值。

S=0, R=0 - Q=1, & Q ' =1[无效]

如果S和R的值都被切换到0,这是一个无效的状态,因为Q和Q '的值都是1。它们应该是彼此的赞美。正常情况下,这种状态必须避免。

S=1 R=1 - Q & Q ' =记住

如果S和R的值都切换为1,则电路会记住S和R在其先前状态下的值。

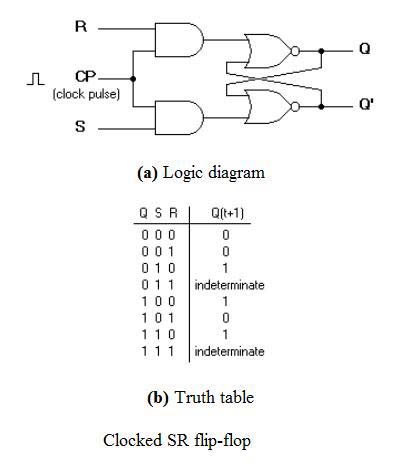

时钟S-R触发器

它也被称为门控S-R触发器。

使用NOR和NAND门的S-R触发器的问题是无效状态。这个问题可以通过使用双稳态SR触发器来克服,它可以在满足某些无效状态时改变输出,不管Set或Reset输入的条件是什么。为此,设计了一个时钟S-R触发器,在基本NOR门触发器上增加两个和门。电路图和真值表如下所示。

时钟脉冲[CP]被提供给与门的输入端。当时钟脉冲值为“0”时,“和”门的输出保持为“0”。一旦给出一个脉冲,CP的值即变为“1”。这使得S和R处的值通过或非门触发器。但当S和R值都变为“1”时,CP的高值会导致它们在短时间内都变为“0”。一旦脉冲被移除,触发器状态变为中间状态。因此,可能会导致这两种状态中的任何一种,这取决于触发器的set或reset输入是否比脉冲结束时转换为“0”的时间长“1”。因此,可以消除无效状态。

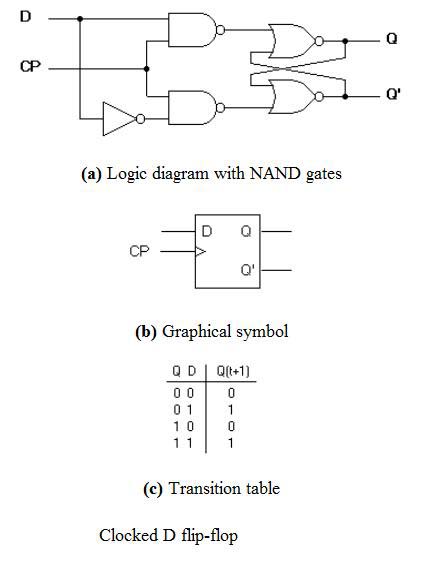

2.D触发器

电路图和真值表如下所示。

D触发器实际上是对上述时钟SR触发器的一个轻微修改。从图中可以看出,D输入连接到S输入,D输入的补码连接到R输入。当CP值为“1”时,D输入被传递到触发器。当CP为高时,触发器移动到设置状态。如果为“0”,触发器将切换到清除状态。

要了解触发器触发的更多信息,请单击下面的链接。

看一看:触发触发器

看一看:主从触发器电路

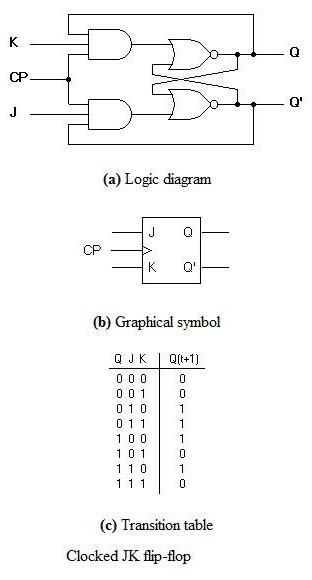

3.j - k触发器

J-K触发器的电路图和真值表如下图所示。

J-K触发器也可以定义为S-R触发器的修改。唯一的区别是中间状态比S-R触发器更精细和精确。

输入J和K的行为与S-R触发器的S和R输入相同。字母J代表SET,字母K代表CLEAR。

当输入J和K均为HIGH状态时,触发器切换到补码状态。当Q=1时,它会切换到Q=0当Q=0时,它会切换到Q=1。

该电路包括两个3输入和门。触发器的输出Q与其他输入如K和时钟脉冲[CP]一起作为反馈返回到AND的输入。所以,如果CP的值是1,触发器得到一个CLEAR信号,条件是Q的值早于1。类似地,触发器的输出Q '与其他输入(如J和时钟脉冲[CP])一起作为与的输入的反馈。因此,只有当Q '的值早于1时,CP的值为1时,输出变成SET。

由于JK触发器中的反馈连接,一旦J=K=1的输出得到称赞,则可以在转换中重复输出。这可以通过设置小于通过触发器的传播延迟的持续时间来避免。通过主从或边缘触发结构,可以消除对脉冲宽度的限制。

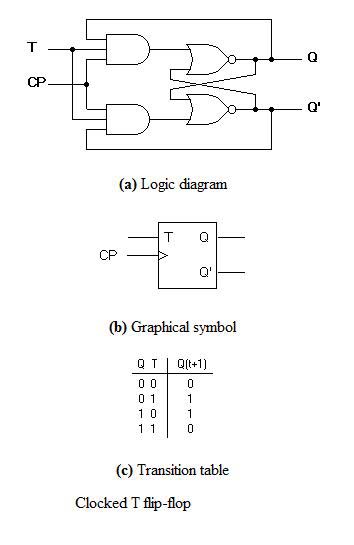

4.T触发器

这是J-K触发器的一个更简单的版本。J和K输入都连接在一起,因此也称为单输入J-K触发器。当时钟脉冲给触发器时,输出开始切换。在这里,对脉冲宽度的限制也可以通过主从或边触发结构来消除。看看下面的电路和真值表。

66评论

你的rs或flipflop真值表是不正确的,它是为rs和flipflop

对流感的简明解释失败了。和我在大学时的想法完全不同。

非常感谢你的信息

Nand fr flip flop让我很困惑,但是其他的都很好学。...

干得好,冀先生

很感伤ɗ文章!我们在我们的网站上链接到这篇伟大的文章。

继续写下去。

关于人字拖的惊人解释。在读完这篇文章后能够理解这些概念:)

你好谢谢这篇发人深省的文章,我并没有真正读过,但确实提醒了我出去,用一些拖鞋。

我想知道在设计一个时钟s-r触发器????时真值表是如何形成的解码器的y1,y2 i.e.o/p是如何发生的??

CP是什么?

谢谢所有的

什么是filp flops

我现在能理解flip flop......了

比如深入的解释。

是否有人,或是否有人,用反馈项,写下了Booloean方程,类似于:

Q (N + 1) = Q (N)。

并且愿意把它寄出去?

感谢

古德解释说,但我的问题是如何从真值表构建一个RS-Flipflop。我的意思是,它更像是一种组合逻辑。

设计rs触发器?

这是对Flip-Flop很好的解释。但我的问题是,我们如何从真值表中制造rs触发器,假设我们之前没有见过电路或者我们必须设计一个电路?如何设计一个顺序逻辑电路呢?

在T和其中一个和门之间不应该有一个逆变器吗?

伟大的工作的人;希望很多人会花时间阅读这篇文章。然而,我发现您在所有时钟FFs中使用了基本触发器的NOR实现。我没有偷懒,你能不能用基本FF的NAND版本来设计这些电路。再次感谢发布的伟大工作

拉里

谢谢你,非常有用................

非常感谢,继续加油,亲爱的

你做得很好,现在我能更好地理解如何出色地写我的考试了<

你做得很好

它很容易阅读和理解

我需要每个人字拖的优点和缺点

我需要每个人的优点和缺点。

优秀的解释

对人字拖的很好的解释

巨大的工作

坚持下去

PLZ还显示波形作为每个触发器的一个例子

非常感谢。

你好,解释一下。爱死它了。

甜蜜的和短。很适合为考试复习,尤其是当你在考试前几个小时学习。

准确而且很有帮助

我知道我不是唯一的一个!

干得好!坚持下去…我喜欢它…

我需要一个激励触发器对所有4个触发器

我喜欢它!!!

简单易懂

先生

在时钟反转技术中,有两个带时钟的与门或两个带时钟脉冲的与非门。但问题是Gate的使用背后的逻辑是什么。

D flip flop也是一样。

实际上我不明白哪个门必须使用,哪个反馈连接到输入(在JK触发器的情况下,某处Q '反馈到J, Q反馈到K)

我需要完美真值表为4类型的人字拖…

似乎在D触发器Drowing上有一个错误,将NAND门改为AND,或将NOR改为NAND。

目前NOR gats在无效输入上有1,1

我试图找到激励表的触发器,但我不能…:(…!!

所以试着把这一点添加到…。!!!

简单的问题有简单的答案……

很好,你把这个话题讲得非常简单易懂

主仆关系的重要性是什么?

未上锁的触发器和锁存器有什么区别

真的好可以再详细说说....但还是不错的

我要别针号码。S表示上图。

感谢您提供有关简单语言中触发器的信息。

谢谢

j.k.f的结构是错误的!!!!!

数字逻辑电路中有三种边缘触发触发器,即SR、D和J-K,每种触发器都有自己的操作。说明这些触发器如何对同步系统的性能产生影响,并讨论哪种触发器的性能更好?给出支持你答案的论据。

非常感谢……

我们的主从关系图是什么?

谢谢……

tanq……

谢谢你的帮助

脉冲宽度和触发器的输出响应之间的关系是什么。

位的减法、除法是什么门?既然半加法器允许两位加和,全加法器允许两位加和和一个进位?

我需要verilog HDL教程…

去买一辆MORIS MANO吧…

Jasa设置Mikrotik Jasa设置代理

谢谢你的帮助。

我非常喜欢它,它对我的作业非常有用

我没有从其他网站找到这些数据,这是非常好的

触发器的用途是什么?时钟脉冲是什么意思?

触发器的用途是什么?时钟脉冲是什么意思

这里提供的信息很容易理解和有用

非常感谢……这些都是非常有用的答案。